数字系统设计-知识点总结

本文最后更新于 2025年6月4日 晚上

数字系统设计-知识点总结

本文是BUL EE2634 Digital Systems Design and Reliability Engineering 数字系统部分的知识点总结。

逻辑门的晶体管实现

晶体管在数字电路中用做开关,实现数字逻辑。有两种最基本的晶体管:NMOS和PMOS。

对于NMOS,如果栅极处于高电平,那么晶体管导通,如果处于低电平,晶体管关断。

PMOS的行为和NMOS完全相反,在电路符号中栅极处多了一个∘。

CMOS晶体管电路是使用PMOS和NMOS的混合电路,其优点在于相比于PMOS和NMOS电路,CMOS在表达数字逻辑“0”或“1”时电路中只有电压的变化,始终没有任何电流的变化,因此理论下在表达过程中不会有任何的功率损失。此外还有高阻抗,匹配功率范围广的优势。因此CMOS被广泛运用。

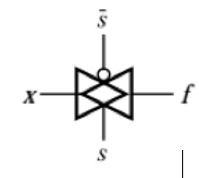

传输门

传输门由一个PMOS和一个NMOS组成,其作用相当于一个开关,电路表示如下图所示:当控制信号\(s=0\)时,电路开路,输出\(f=0\)。当控制信号\(s=1\)时,电路闭合,\(f=x\)。

逻辑门的晶体管数量

实现各逻辑门所含晶体管数量如下表所示:

| 逻辑门 | NOT | 2NAND | 2NOR | 2AND | 2OR | 传输门 |

|---|---|---|---|---|---|---|

| 晶体管数量 | 2 | 4 | 4 | 6 | 6 | 2 |

对于CMOS电路而言,每增加一个输入,就会分别增加一个PMOS和NMOS,因此\(n\)个输入的NAND或者NOR门需要的晶体管数目为:

\[\#transistors=2n\] AND门和OR门是在NAND和NOR的基础上增加一个NOT门,NOT含有两个晶体管,因此\(n\)个输入的AND或者OR门需要的晶体管数目为:

\[\#transistors=2n+2\]

系统的逻辑表达

系统的逻辑表达式有两种:SOP(Sum of Product)和POS(Product of Sum)。 SOP可以用全部用NAND门表达:

\[A.B+C.D=\overline{(\overline{A}.\overline{B}).(\overline{C}.\overline{D})}\]

POS可以全部用NOR门表达:

\[(A+B).(C+D)=\overline{\overline{A+B}+\overline{C+D}}\]

减少成本的方式/化简数字电路的方式

数字系统设计中最核心的实现是减少系统设计的成本(Cost),数字电路的成本可以用门成本表示:

\[Cost=\#inputs+\#gates\] 其中\(inputs\)指电路中所有门的输入数,\(gates\)是电路中所有逻辑门的数量。需要注意的是,只有在“非”逻辑下方有非逻辑时(比如:\(\overline{A+\overline{A}B}\)),才将NOT门及其输入计入\(gates\)和\(inputs\)。

逻辑运算律化简

通过逻辑运算律进行化简,几个重要的逻辑运算律:

- 吸收律: \(A+AB=A\)

\(A(A+B)=A\) - 德摩根律: \(\overline{AB}=\overline{A}+\overline{B}\)

\(\overline{A+B}=\overline{A}.\overline{B}\)

卡诺图化简

- SOP圈“1”,“1→x”

- POS圈“0”,“0→x”

- 每个圈中的蕴含项个数只能为\(2^n\)

- 尽可能圈住最多的蕴含项

- 四个边视为相邻,四个角视为相邻

- 如果一个圈里面所有的蕴含项都在其他圈中出现,这个圈可以被取消

- 通配符“d”可以被圈住

- 一个电路多个输出时,对多个输出分别画卡诺图,多张卡诺图中圈的位置尽可能相同。

如果题目中的设计目标是“最小成本”,那么做完卡诺图化简后还需要提取公因项化简。

如果题目中的设计目标是“最简SOP/POS”,那么做完卡诺图化简后即可。

逻辑电路元件

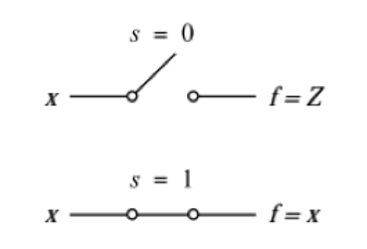

加法器

半加器为不含进位的加法器,全加器相比于半加器有另一个输出用于表示进位。

加法器可以通过列出真值表,对进位(carry)和和(sum)分别用卡诺图化简即可。

第\(i+1\)位的进位表示为:

\[c_{i+1}=x_iy_i+x_ic_i+y_ic_i\] 第\(i\)位的和表示为:

\[s_i=x_i⊕y_i⊕c_i\] 如果将加法器的其中一个输入和一个控制信号与异或门连接,就能将这个输入在控制信号为0时转为二补码,实现两个输入的减法。

多路复用器

多路复用器是一种通过控制信号,实现从多个输入信号中选择一个信号输出的数字电路器件。当输入信号为从00..0到11..1的不同组合时,多路复用器会对应输出其结果,利用这一特性可以让多路复用器实现逻辑表达式。

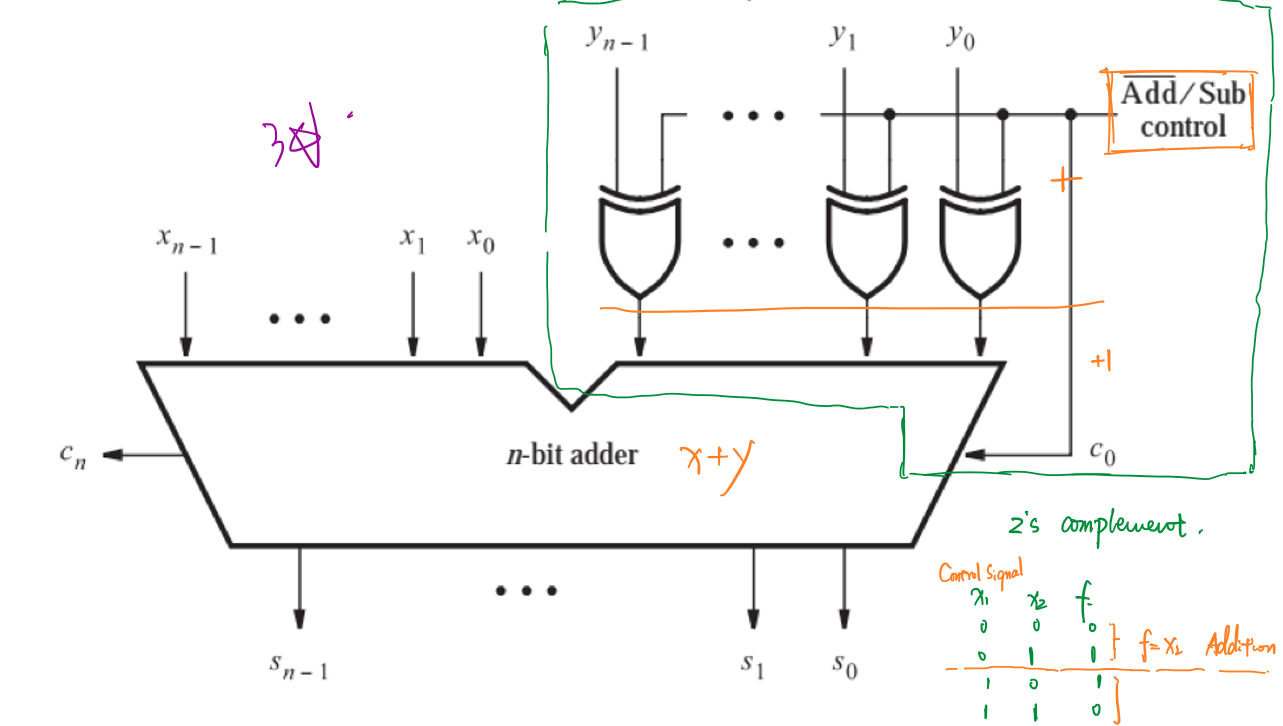

解码器·编码器

解码器是一种输入\(n\)个比特,返回对应的\(2^n\)个比特值的电路器件。编码器的行为和解码器相反,输入\(2^n\)个比特,返回\(n\)个比特的器件。

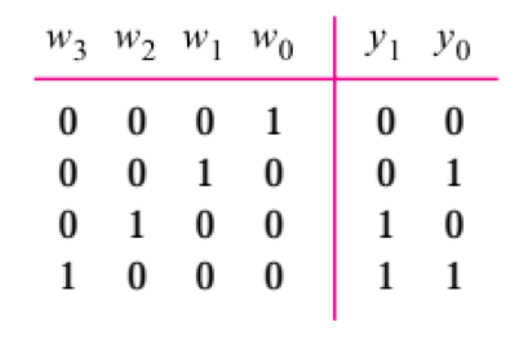

对于解码器,当\(En=1\)时,输入\(w_1w_0\)为特定的比特组合时,输出端对应的输出为1,其余输出为0.其真值表如下:

编码器的行为和解码器完全相反:

比较器

比较器在一个电路中可以实现对两个输入信号\(A\),\(B\)的比较,并用布尔值返回其比较结果。比较器有三个输出结果:\(AeqB,AgtB,AleB\),\(A\)和\(B\)满足哪一个关系,比较器对应的输出结果就是1。

\(AeqB\)

判断A和B是否相等的简单思路是利用XOR门的特性逐位比较每一个比特是否相同,但是XOR门在相同时输出结果为0,因此最后还需要取反才能得到每一位正确的比较结果。每一个比特位的比较可以表示为:

\[i_k=\overline{a_k⊕b_k}\] 当所有位都相同时,\(AeqB=1\): \[AeqB=i_ni_{n-1}...i_1i_0\]\(AgtB\)

在每一个比特位上,只有\(a_i=1\),\(b_i=0\)时才能判断在该位上\(a_i>b_i\)。\(AgtB\)表示为:

\[AgtB=a_n\overline{b_n}+i_na_{n-1}\overline{b_{n-1}}+i_ni_{n-1}a_{n-2}\overline{b_{n-2}}+...+∏_{i=1}^ni_ka_0\overline{b_0}\]\(AleB\) 当A既不大于B,也不等于B时,其结果为\(A<B\): \[AleB=\overline{AgtB+AeqB}\]

逻辑电路的实现方式

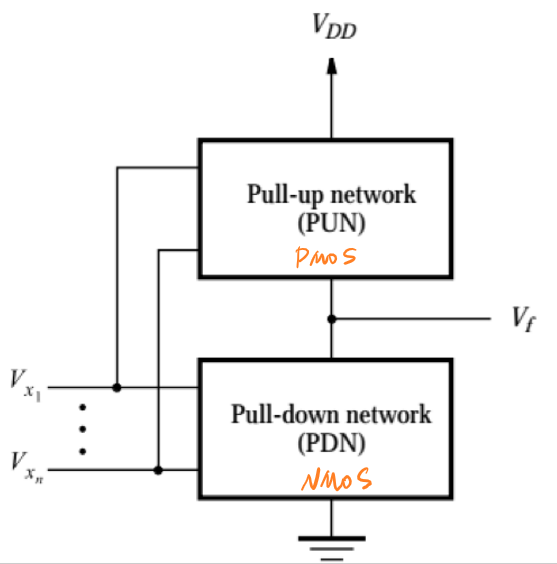

CMOS电路

CMOS电路由两部分构成:上拉和下拉电路。

上拉电路由PMOS管组成,电路上端接\(V_{dd}\),当一条回路上的PMOS全部导通时,对应的输出为1。

下拉电路由NMOS管组成,电路下端接地,当一条回路上的NMOS全部导通时,对应的逻辑输出为0。

使用CMOS电路实现逻辑表达式的思想是:

- 逻辑表达式中的每一项对应电路中的一条支路。

- 对于每一项,AND逻辑用串联电路构建,OR逻辑用并联电路实现。

- 对于上拉电路,应当用POS表达\(f\)。

- 对于下拉电路,应当对上拉电路的表达式取反\(\overline{f}\),用德摩根律化简。

多路复用器电路

从逻辑表达式实现多路复用器电路的过程:

- 看输入信号的数量,并选取其中一些输入信号的作为控制信号。 控制信号的数量满足:

\[2^{控制信号的数量} ≥ 剩余输入信号的数量\] - 利用香农展开,从逻辑表达式中提取出一个控制信号,并将逻辑表达式写作如下形式:

\[f(w_1,w_2,..,w_n)=\overline{w_1}f(0,w_2,...,w_n)+w_1f(1,w_2,...,w_n)\] - 再从\(f(0,w_2,...,w_n)\)和\(f(1,w_2,...,w_n)\)使用相同的方法提取出第二个控制信号,重复直到所有的控制信号都被提取。

移位器(Shifter)电路

移位器设计的关键是写出不同的控制信号对应的每一位上的输出,列表。然后竖着看表,根据每一位输出在不同控制信号下对应的输出,对这个输出用多路复用器搭建电路。重复直到每一个输出都用一个对应的多路复用器电路表达,然后将相同的输入连接到一起即可。

解码器电路

SOP可以直接用解码器电路表达,如果在SOP中最小项\(i=1\),那么解码器电路中的\(y_i\)需要被输出,解码器中所有的\(y_i\)用OR门相连,剩下的输出端口不需要输出。

查找表(LUT)电路

单级的查找表只需要写明输入信号,并在寄存器图标上填入真值表的输出即可。

多级的查找表电路需要利用香农展开,提取变量作为控制信号后,对括号内的项构建查找表电路,再使用输出和控制信号构建下一级的查找表电路。

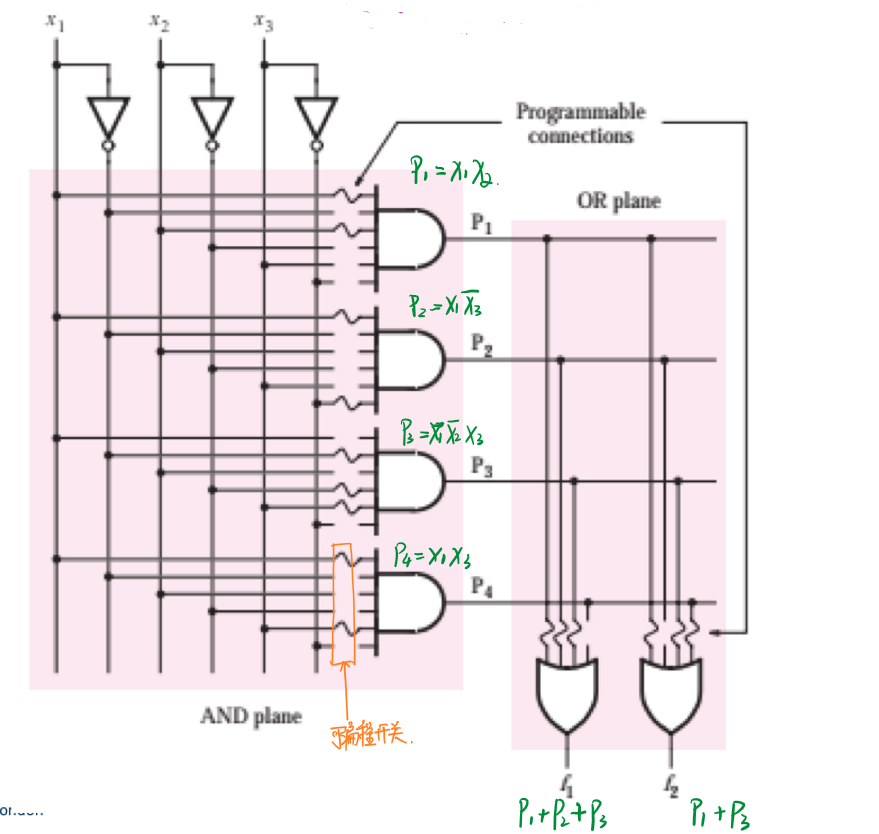

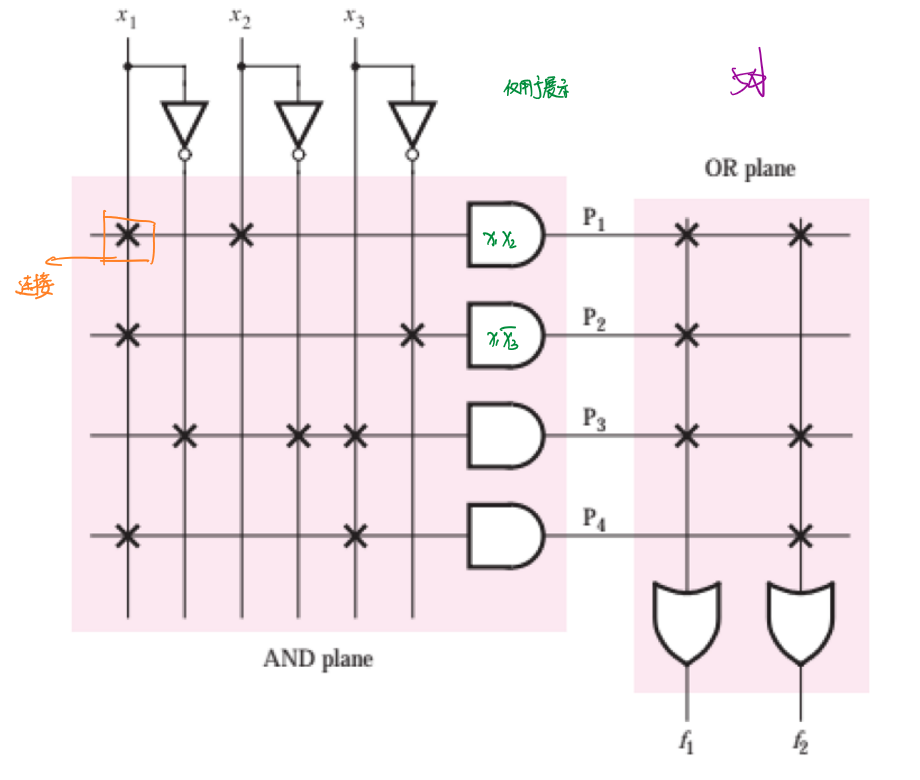

可编程逻辑阵列(PLA)和可编程阵列逻辑(PAL)

可编程逻辑阵列(PLA)和可编程阵列逻辑(PAL)中逻辑门的输入端存在可编程开关,因此可以通过控制开关的开闭来实现不同的布尔函数。

可编程逻辑阵列(PLA)实现的是先AND,再OR的SOP逻辑,例子如下图所示:

在可编程逻辑中,电路中的“×”代表此处是连接的。

在PLA当中,电路中OR门所在的区域(称为OR平面)是固定好的,不可以被编程。

可编程开关的劣势:

- 影响运行速度

- 占据大量空间

- 增加功耗

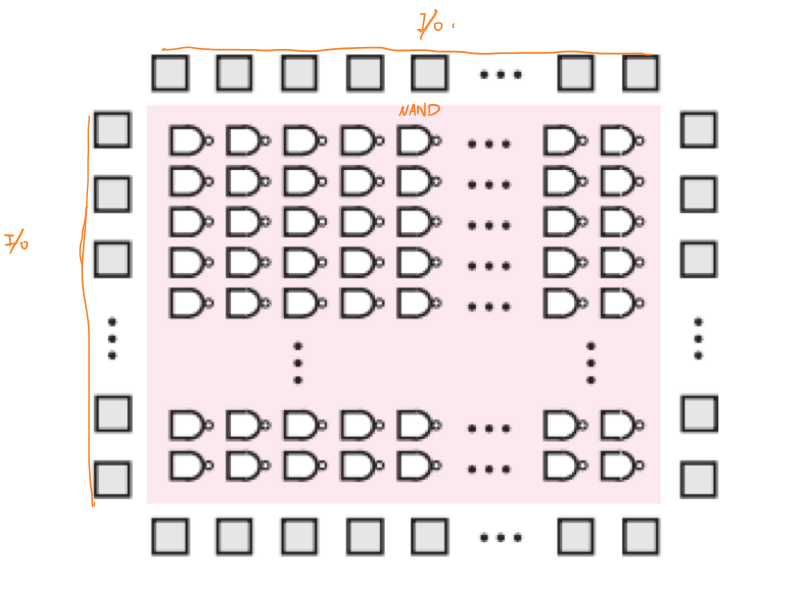

门阵列

门阵列中,阵列外围是输入或者输出端口,其内部为位置固定的NAND门或者NOR门的阵列,可通过将端口和逻辑门连接实现对应的NAND-only或NOR-only的布尔表达式。

锁存器和触发器

锁存器(Latch)是一类有记忆功能的数字电路器件。触发器在锁存器的基础上被构建出来。

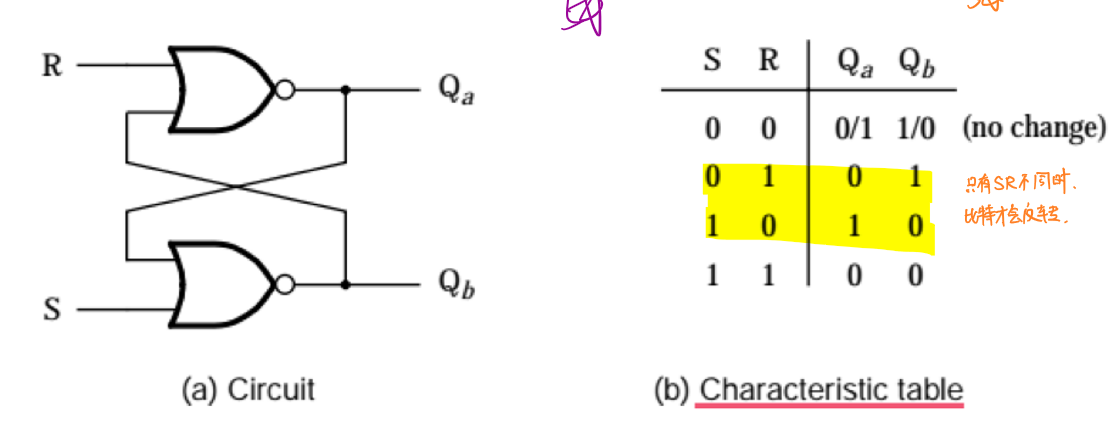

RS锁存器

RS锁存器的电路结构和真值表如下图所示:

其表现归纳为:“只有SR处于不同值时,对应输出为1”。

SR锁存器的问题是当\(S=1,R=1\)时,\(Q_a=1,Q_b=1\),如果此时设置\(S=0,R=0\)时,触发器的输出\(Q_a=0,Q_b=0\),并作为下一次的输入,此时\(Q_a=1,Q_b=1\),接下来,锁存器将处于不断的0-1跳变当中。

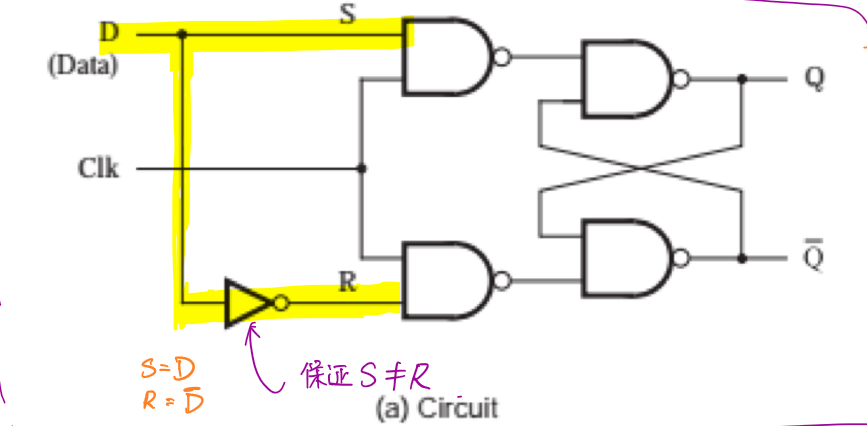

D锁存器

RS锁存器存在跳变的解决办法是使用一个输入D来代替原来的RS两个输入端口,并使用一个NOT门让D输入的一条支路的逻辑值反转,对于整个电路而言,就永远不可能出现SR值相同的情况,进而无法出现跳变。此外,D锁存器加入了时钟信号clk,使得当时钟信号为0时,锁存器当永久保存当前的输出状态,直到时钟信号变为1。

其真值表为:

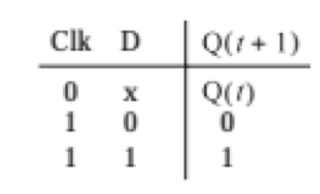

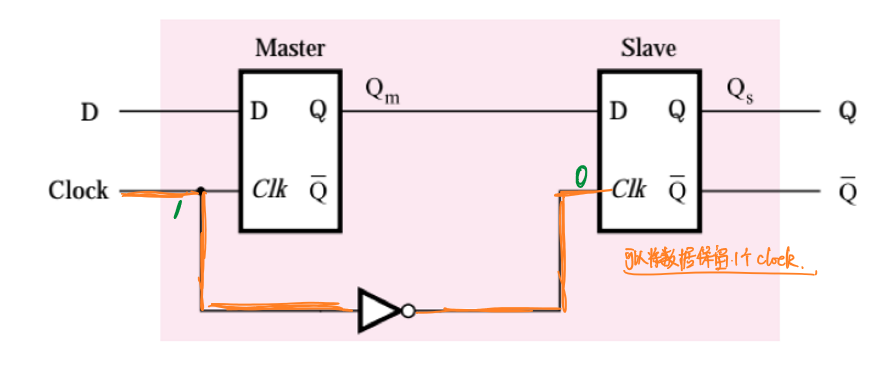

主从D触发器

主从D触发器能够保留一个时钟的信息,其结构如下图所示:

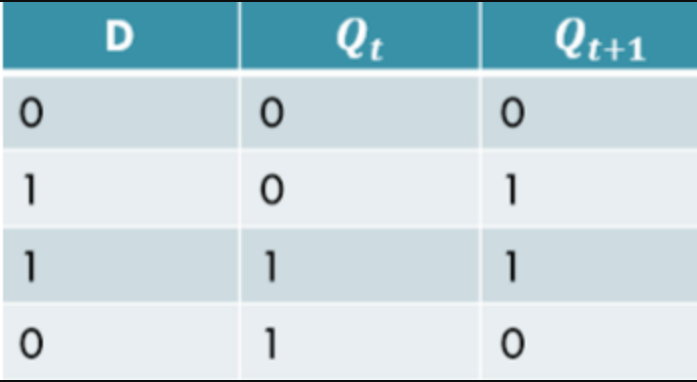

D触发器的真值表为:

D触发器的行为规则是:

- 在clk=1的时刻,其输出随着D的变换而变化。

- 在clk=0的时刻,其输出保留之前的状态。

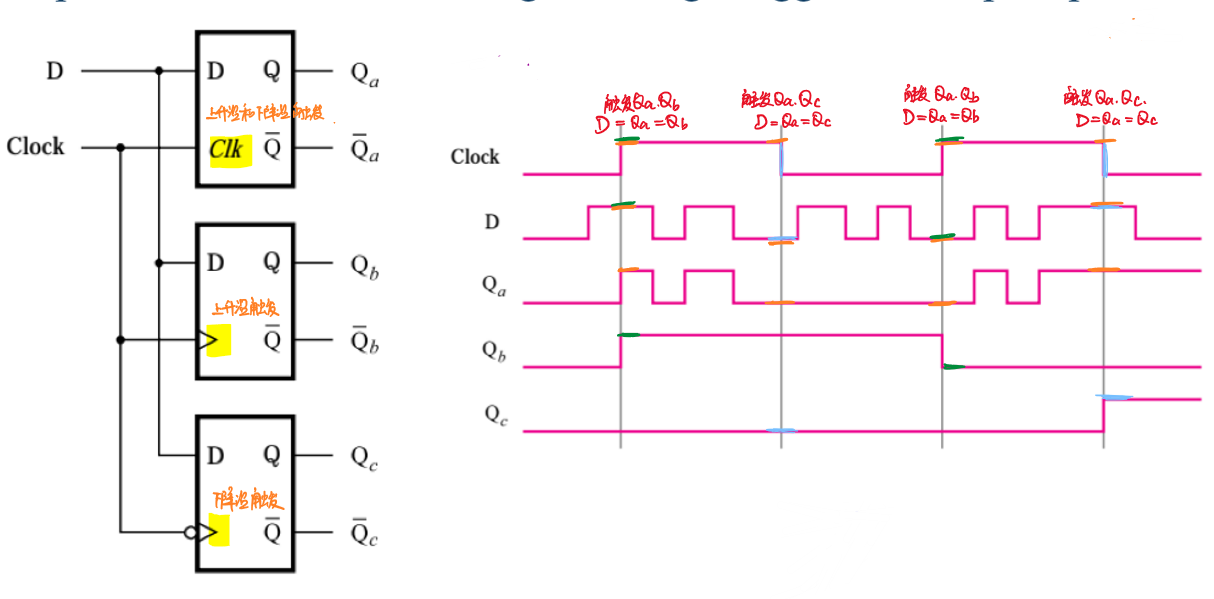

D触发器的触发规则有上升沿触发、下降沿触发,不同的触发方式对于同一个输入信号,其结果可能是不同的:

- 对于D锁存器/主从D触发器,其在clk=1的时刻与D完全同步变化。在clk=0的时刻,其输出保留之前的状态

- 对于上升沿D触发器,其始终保留在clk=1的上升沿前最后一个D,直到下一个clk=1的上升沿出现。

- 对于下升沿D触发器,其始终保留在clk=1的下降沿前最后一个D。直到下一个clk=1的下降沿出现。

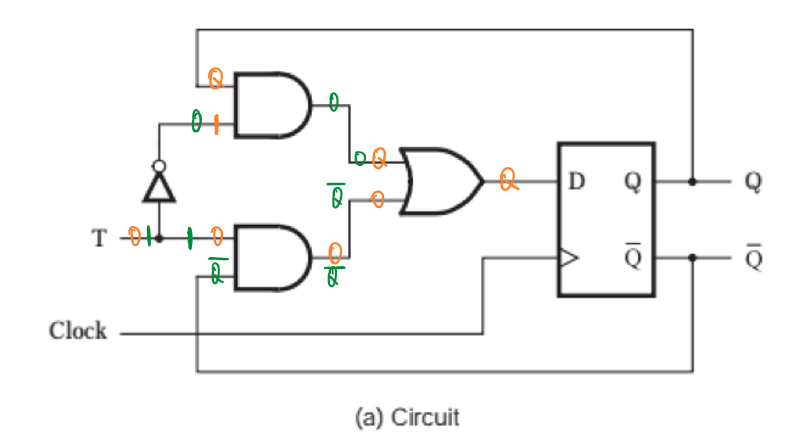

T触发器

T触发器的结构如下图所示:

T触发器的真值表为:

其clk=1的时间中,其行为为:

T=1时发生比特反转,T=0时保留原来的比特。

JK触发器

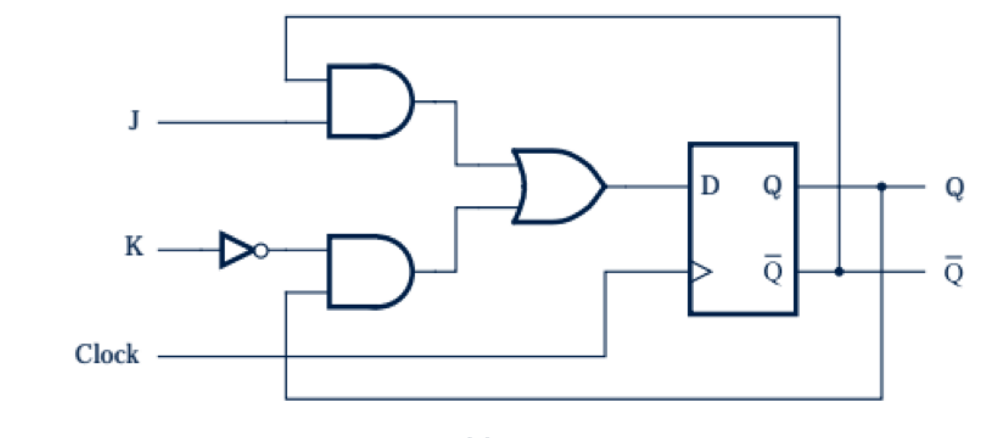

JK触发器是SR触发器和D触发器的变形,其结构为:

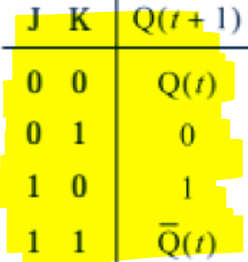

JK触发器的真值表为:

其行为可以描述为:

- JK=1时,输出\(\overline{Q}\)。JK=0时,输出\(Q\)。

- J代表set,仅\(J=1\)时,\(Q\)强制为1。

- K代表reset,仅\(K=1\)时,\(Q\)强制为0。

VHDL程序基础

VHDL是一种用于描述逻辑电路的程序,程序的基本结构由用于声明输入和输出端口的ENTITY和用于描述逻辑电路功能的ARCHITECTURE组成。

ENTITY的写法如下例程所示,这段例程program1声明了\(x_1\),\(x_2\),\(x_3\)是输入变量,其数据类型为STD_Logic(standard logic,此处的数据类型也可以是BIT),并指定输出端口为\(f\):

1

2

3

4ENTITY program1 IS

PORT(x1,x2,x3 : IN STD_Logic;

f : OUT STD_Logic;);

END program1 ;<=表示赋值。

下面的例程中展示了program1是如何实现\(f=x_1x_2+\overline{x_2}x_3\)的:

1

2

3

4ARCHITECTURE LogicFunc OF program1 IS

Begin

f<= (x1 AND x2) OR (NOT x2 AND x3);

END LogicFunc;

在VHDL中,逻辑运算是没有优先级的,需要通过给定括号()来制定优先级。

此外,VHDL语言中还支持使用分支结构来表达:

分支结构中使用WHITH声明控制变量,使用WHEN 'bit'和WHEN OTHERS来指定控制信号为对应比特值bit时和其他时候的对应的情况。

需要注意最后一种情况对应的一定是WHEN OTHERS以排除可能出现的所有不稳定值。

比如下面例程所示的2-1多路复用器,当输入信号\(s=0\)时,\(f=w_1\),\(s=1\)时,\(f=w_2\)。

1

2

3

4

5

6

7

8

9

10

11

12

13

14LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY mux2to1 IS

PORT(w0,w1,s IN STD_logic

f OUT STD_logic);

END mux2to1;

ARCHITECTURE behavior OF mux2t01 IS

BEGIN

WITH s SELECT

f<=w1 WHEN '0';

f<=w0 WHEN OTHERS;

END behavior;STD_logic和BIT之外,VHDL还支持STD_logic_vector()这样的逻辑向量表达,有升序:STD_logic_vector(m TO n)表示从m 到 n的比特值组成的向量,和降序:STD_logic_vector(n DOWNTO m)两种。字节长度在ACHITECURE中指定。

比如下面例程所示的2-4解码器: 1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY dec2to4 IS

PORT(

w : IN STD_logic_vector(1 DOWNTO 0);

En : IN STD_logic;

y : OUT STD_LOGIC_VECTOR(0 TO 3);

)

END dec2to4;

ARCHITECUTURE behavior OF dec2t04 IS

SIGNAL Enw: STD_logic_vector(2 DOWNTO 0);

BEGIN

Enw <= En AND w;

WITH Enw SELECT

y <= "1000" WHEN "100",

"0100" WHEN "101",

"0010" WHEN "110",

"0000" WHEN OTHERS;

END behavior;